# Working Draft

## T10.1/1146D

Revision 5c November 3, 1997

## Information Technology - Serial Storage Architecture - Physical Layer 2 (SSA-PH2)

Draft proposed American National Standard

This is a draft proposed American National Standard of Accredited Standards Committee NCITS. As such, this is not a completed standard. The T10 Technical Committee may modify this document as a result of comments received during public review and its approval as a standard.

Permission is granted to members of NCITS, its technical committees, and their associated task groups to reproduce this document for the purposes of NCITS standardization activities without further permission, provided this notice is included. All other rights are reserved. Any duplication for commercial or for-profit use is prohibited.

#### **ABSTRACT**

This standard describes the Serial Storage Architecture Physical Layer 2 (SSA-PH2). SSA defines a serial interface hierarchy to be used for purposes within its distance and performance characteristics, including but not limited to storage subsystems.

The Serial Storage Architecture fills a need in the evolution from parallel to serial interfaces for storage devices. It meets the space constraints and cabling considerations for high-density storage arrays with a commensurate improvement in reliability (an architected error recovery, redundant paths to devices, a wrap mode for self-test, line fault detection and a balanced signaling scheme that achieves a low error rate) and configurability (the ability to hot-plug devices, the self-configuration capability, the 20 meter length of cable segments).

The physical layer allows for a CMOS implementation to achieve an economical and small package size, an efficient use of bandwidth, a small frame size to reduce buffer expense and the capability for self-configuration are also needed. The physical requirements include 20 meter distance per cable segment, a small number of signals to limit connector and cable expense, and a low voltage implementation.

Project Leader Technical Editor

Dan Tsai John P. Scheible

IBM Corporation IBM Corporation

5600 Cottle Road Bldg 902, M/S 9263

Dept. RWWA, Bldg 050 11400 Burnet Road

San Jose, CA 95193 Austin, TX 78758

Voice:

(408) 256-5729

Voice:

(512) 823-8208

Fax:

(408) 256-0595

Fax:

(512) 838-3822

Email: tsaidaniel@vnet.ibm.com Email: scheible@vnet.ibm.com

Other Points of Contact:

T10.1 Chairman

Lawrence Lamers

Adaptec

MS 293

Bldg 902, M/S 9263

691 South Milpitas Blvd

Milpitas, CA 95035

T10.1 Vice-Chairman

John P. Scheible

IBM Corporation

Bldg 902, M/S 9263

11400 Burnet Road

Austin, TX 78758

Voice: 408-957-7817 (512) 823-8208 Fax: 408-957-7193 (512) 838-3822

Email: ljlamers@aol.com scheible@vnet.ibm.com

**NCITS Secretariat**

Administrator Standards Processing

NCITS Secretariat

Voice:

202-737-8888

1250 Eye Street, NW

Suite 200

FAX:

202-638-4922

Washington, DC 20005 Email: NCITSsec@itic.nw.dc.us

SSA Reflector

Internet address for subscription to the T10.1 reflector: majordomo@symbios.com

Note should contain a line stating... subscribe T10-SSA your email address

Internet address for distribution via T10.1 reflector: t10-ssa@symbios.com

T10 Bulletin Board 719-533-7950

FTP Site: ftp.symbios.com

/pub/standards/io/t10.1

Web sites: http://www.NCITS.org/t10

or http://www.symbios.com/t10

http://www.ssaia.org

**Document Distribution**

Global Engineering

Voice:

303-792-2181

15 Inverness Way East

or:

800-854-7179

Englewood, CO 80112-5704

FAX:

303-792-2192

#### **PATENT STATEMENT**

CAUTION: The developers of this standard have requested that holder's of patents that may be required or the implementation of the standard, disclose such patents to the publisher. However, neither the developers nor the publisher have undertaken a patent search in order to identify which, if any, patents may apply to this standard.

As of the date of publication of this standard, following calls for the identification of patents that may be required for the implementation of the standard, notice of one or more claims has been received.

By publication of this standard, no position is taken with respect to the validity of this claim or of any rights in connection therewith. The known patent holder has, however, filed a statement of willingness to grant a license under these rights on reasonable and nondiscriminatory terms and conditions to applicants desiring to obtain such a license. Details may be obtained from the publisher.

No further patent search is conducted by the developer or the publisher in respect to any standard it processes. No representation is made or implied that licenses are not required to avoid infringement in the use of this standard.

American National Standard for Information Technology -

Serial Storage Architecture - Physical Layer 2 (SSA-PH2)

Secretariat

**Information Technology Industry Council**

Approved Month dd, yy

American National Standards Institute, Inc.

#### **Abstract**

This standard describes the Serial Storage Architecture Physical Layer 2 (SSA-PH2). SSA defines a serial interface hierarchy to be used for purposes within its distance and performance characteristics, including but not limited to storage subsystems.

The Serial Storage Architecture fills a need in the evolution from parallel to serial interfaces for storage devices. It meets the space constraints and cabling considerations for high-density storage arrays with a commensurate improvement in reliability (an architected error recovery, redundant paths to devices, a wrap mode for self-test, line fault detection, and a balanced signaling scheme that achieves a low error rate) and configurability (the ability to hot-plug devices, the self-configuration capability, the 20 meter length of cable segments).

The physical layer allows for a CMOS implementation to achieve an economical and small package size, an efficient use of bandwidth, a small frame size to reduce buffer expense, and the capability for self-configuration are also needed. The physical requirements include 20-meter distance per cable segment, a small number of signals to limit connector and cable expense, and a low-voltage implementation.

### American National Standard

Approval of an American National Standard requires review by ANSI that the requirements for due process, consensus, and other criteria for approval have been met by the standards developer. Consensus is established when, in the judgment of the ANSI Board of Standards Review, substantial agreement has been reached by directly and materially affected interests. Substantial agreement means much more than a simple majority, but not necessarily unanimity. Consensus requires that all views and objections be considered, and that a concerted effort be made towards their resolution.

The use of American National Standards is completely voluntary; their existence does not in any respect preclude anyone, whether he has approved the standards or not, from manufacturing, marketing, purchasing, or using products, processes, or procedures not conforming to the standards,

The American National Standards Institute does not develop standards and will in no circumstances give interpretation on any American National Standard. Moreover, no person shall have the right or authority to issue an interpretation of an American National Standard in the name of the American National Standards Institute. Requests for interpretations should be addressed to the secretariat or sponsor whose name appears on the title page of this standard.

**CAUTION NOTICE**: This American National Standard may be revised or withdrawn at any time. The procedures of the American National Standards Institute require that action be taken periodically to reaffirm, revise, or withdraw this standard. Purchasers of American National Standards may receive current information on all standards by calling or writing the American National Standards Institute.

CAUTION: The developers of this standard have requested that holder's of patents that may be required or the implementation of the standard, disclose such patents to the publisher. However, neither the developers nor the publisher have undertaken a patent search in order to identify which, if any, patents may apply to this standard.

As of the date of publication of this standard, following calls for the identification of patents that may be required for the implementation of the standard, notice of one or more claims has been received. By publication of this standard, no position is taken with respect to the validity of this claim or of any rights in connection therewith. The known patent holder has, however, filed a statement of willingness to grant a license under these rights on reasonable and nondiscriminatory terms and conditions to applicants desiring to obtain such a license. Details may be obtained from the publisher.

No further patent search is conducted by the developer or the publisher in respect to any standard it processes. No representation is made or implied that licenses are not required to avoid infringement in the use of this standard.

Published by

American National Standards Institute

11 West 42nd Street, New York, New York 10036

Copyright 199n by American National Standards Institute All rights reserved.

#### **Contents**

|       |                                                          | Page |

|-------|----------------------------------------------------------|------|

| Fore  | eword                                                    | V    |

| Intro | oduction                                                 | ix   |

| 1     | Scope                                                    | 1    |

| 1.1   | SSA-PH2 characteristics                                  | 1    |

| 1.2   | SSA family of standards                                  | 2    |

| 2     | References                                               | 3    |

| 2.1   | Normative references                                     | 3    |

| 2.2   | Informative references                                   | 3    |

| 3     | Definitions, symbols, and abbreviations                  | 4    |

| 3.1   | Definitions                                              | 4    |

| 3.2   | Symbols and abbreviations                                | 4    |

| 4     | Conventions                                              | 5    |

| 5     | Modulation                                               | 6    |

| 6     | Data Rate                                                | 6    |

| 7     | Electrical requirements                                  | 6    |

| 7.1   | Line driver                                              | 8    |

| 7.2   | Line receiver                                            | 16   |

| 7.3   | Line segment termination                                 | 19   |

| 7.4   | Ground shift                                             | 20   |

| 7.5   | Port connection                                          | 21   |

| 7.6   | System level noise margin                                | 25   |

| 8     | Interconnections                                         | 26   |

| 8.1   | Internal connectors                                      | 26   |

| 8.2   | Internal Port Connections                                | 42   |

| 8.3   | Internal options bay connections                         | 44   |

| 8.4   | Internal device power connections                        | 45   |

| 8.5   | External connections                                     | 46   |

|       |                                                          |      |

| Tab   | oles                                                     |      |

| 1     | SSA physical interconnect schemes                        | 6    |

| 2     | Driver output spectral content                           | 13   |

| 3     | Driver system operating parameters                       | 14   |

| 4     | Driver test parameters                                   | 14   |

| 5     | Line driver operating requirements at the port connector | 14   |

| 6     | Electrical requirements for Line Driver termination      | 15   |

| 7                                                                 | Receiver system operating parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18                                    |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 8                                                                 | Receiver test parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                    |

| 9                                                                 | Receiver operating requirements at the port connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19                                    |

| 10                                                                | Electrical requirements for line segment termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20                                    |

| 11                                                                | Internal connector options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27                                    |

| 12                                                                | Pinouts for internal port device connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42                                    |

| 13                                                                | Pinout for 4-line Internal port device connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43                                    |

| 14                                                                | Pinout for 5-line internal port device connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43                                    |

| 15                                                                | Pinout for 6-line internal port device connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43                                    |

| 16                                                                | TTL input pin parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44                                    |

| 17                                                                | TTL output pin parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 44                                    |

| 18                                                                | Options connector pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 44                                    |

| 19                                                                | Power connector pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46                                    |

| 20                                                                | External micro-miniature D device connector pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50                                    |

| 21                                                                | External micro-miniature D cable pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50                                    |

| 22                                                                | External HSSDC device connector pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 53                                    |

| 23                                                                | External HSSDC cable pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54                                    |

| 24                                                                | Transfer impedance requirements for external SSA connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55                                    |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |

| Fig                                                               | ures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |

| Fig<br>1                                                          | ures Relationship of the SSA standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2                                     |

|                                                                   | Relationship of the SSA standards  Electrical configuration for SSA serial links                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7                                     |

| 1                                                                 | Relationship of the SSA standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                     |

| 1 2                                                               | Relationship of the SSA standards  Electrical configuration for SSA serial links                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7<br>8                                |

| 1<br>2<br>3                                                       | Relationship of the SSA standards  Electrical configuration for SSA serial links  Test points                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7<br>8<br>9                           |

| 1<br>2<br>3<br>4                                                  | Relationship of the SSA standards  Electrical configuration for SSA serial links  Test points  SSA Line Driver implementation example                                                                                                                                                                                                                                                                                                                                                                                                          | 7<br>8<br>9                           |

| 1<br>2<br>3<br>4<br>5                                             | Relationship of the SSA standards  Electrical configuration for SSA serial links  Test points  SSA Line Driver implementation example  Relationship between LineOut currents at the port connector                                                                                                                                                                                                                                                                                                                                             | 7<br>9<br>10                          |

| 1<br>2<br>3<br>4<br>5                                             | Relationship of the SSA standards  Electrical configuration for SSA serial links  Test points  SSA Line Driver implementation example  Relationship between LineOut currents at the port connector  Test environment for drivers                                                                                                                                                                                                                                                                                                               | 7<br>9<br>10<br>11                    |

| 1<br>2<br>3<br>4<br>5<br>6<br>7                                   | Relationship of the SSA standards.  Electrical configuration for SSA serial links.  Test points.  SSA Line Driver implementation example.  Relationship between LineOut currents at the port connector.  Test environment for drivers.  Test environment for driver spectral content.                                                                                                                                                                                                                                                          | 7<br>9<br>10<br>11<br>12              |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8                              | Relationship of the SSA standards  Electrical configuration for SSA serial links  Test points  SSA Line Driver implementation example  Relationship between LineOut currents at the port connector  Test environment for drivers  Test environment for driver spectral content  Driver output spectral content                                                                                                                                                                                                                                 | 7<br>9<br>10<br>12<br>13              |

| 1 2 3 4 5 6 7 8 9                                                 | Relationship of the SSA standards  Electrical configuration for SSA serial links  Test points  SSA Line Driver implementation example  Relationship between LineOut currents at the port connector  Test environment for drivers  Test environment for driver spectral content  Driver output spectral content  SSA driver pulse mask                                                                                                                                                                                                          | 710121313                             |

| 1 2 3 4 5 6 7 8 9 10                                              | Relationship of the SSA standards  Electrical configuration for SSA serial links  Test points  SSA Line Driver implementation example  Relationship between LineOut currents at the port connector  Test environment for drivers  Test environment for driver spectral content  Driver output spectral content  SSA driver pulse mask  Line Driver termination schematic                                                                                                                                                                       | 710131315                             |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10                   | Relationship of the SSA standards  Electrical configuration for SSA serial links  Test points  SSA Line Driver implementation example  Relationship between LineOut currents at the port connector  Test environment for drivers  Test environment for driver spectral content  Driver output spectral content  SSA driver pulse mask  Line Driver termination schematic  SSA receiver test environment                                                                                                                                        | 7<br>10<br>12<br>13<br>13<br>15       |

| 1 2 3 4 5 6 7 8 9 10 11 12                                        | Relationship of the SSA standards  Electrical configuration for SSA serial links  Test points  SSA Line Driver implementation example  Relationship between LineOut currents at the port connector  Test environment for drivers  Test environment for driver spectral content  Driver output spectral content  SSA driver pulse mask  Line Driver termination schematic  SSA receiver test environment  Receiver pulse mask                                                                                                                   | 7<br>10<br>12<br>13<br>15<br>16<br>16 |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13 | Relationship of the SSA standards  Electrical configuration for SSA serial links  Test points  SSA Line Driver implementation example  Relationship between LineOut currents at the port connector  Test environment for drivers  Test environment for driver spectral content  Driver output spectral content  SSA driver pulse mask  Line Driver termination schematic  SSA receiver test environment  Receiver pulse mask  Definition of ground shift                                                                                       | 7101315161820                         |

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14                                  | Relationship of the SSA standards  Electrical configuration for SSA serial links  Test points  SSA Line Driver implementation example  Relationship between LineOut currents at the port connector  Test environment for drivers  Test environment for driver spectral content  Driver output spectral content  SSA driver pulse mask  Line Driver termination schematic  SSA receiver test environment  Receiver pulse mask  Definition of ground shift  Lines and line segments                                                              | 7101315161820                         |

| 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15                               | Relationship of the SSA standards.  Electrical configuration for SSA serial links.  Test points.  SSA Line Driver implementation example.  Relationship between LineOut currents at the port connector.  Test environment for drivers.  Test environment for driver spectral content.  Driver output spectral content.  SSA driver pulse mask.  Line Driver termination schematic.  SSA receiver test environment.  Receiver pulse mask.  Definition of ground shift.  Lines and line segments.  Port connection and Port Connection segments. | 71013151618202121                     |

| 19  | Complex Port Connection examples using PCCs                                  | .25 |

|-----|------------------------------------------------------------------------------|-----|

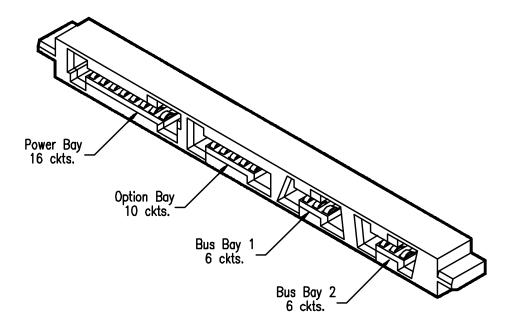

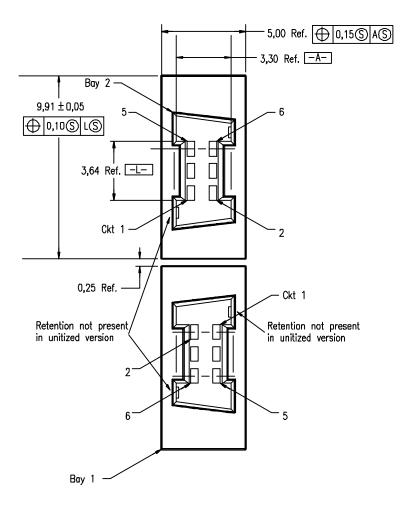

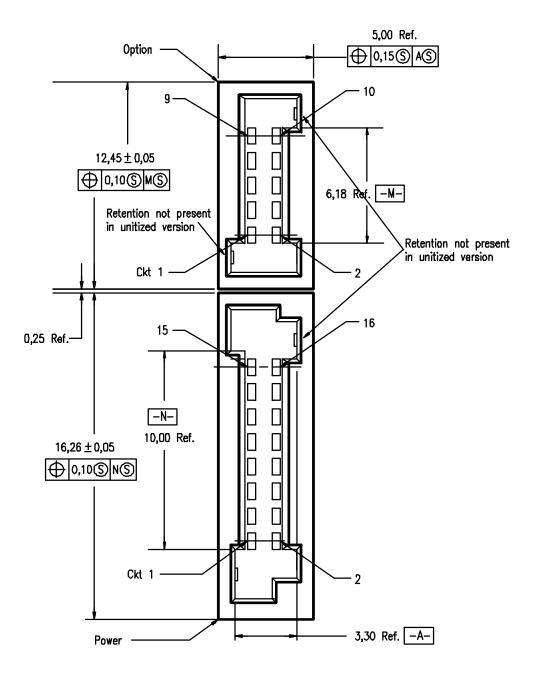

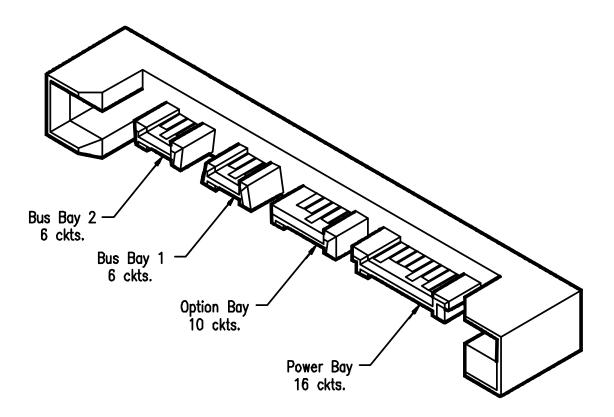

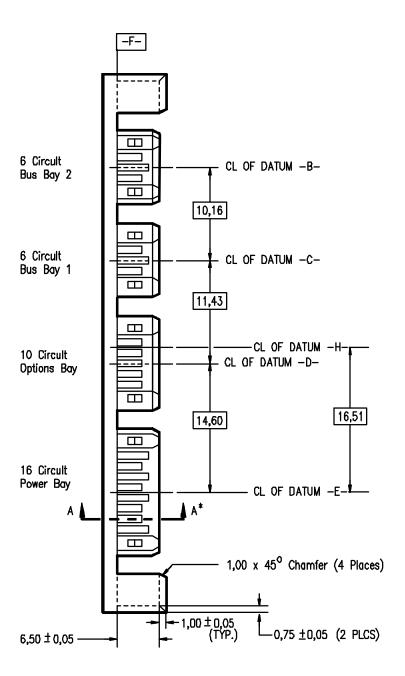

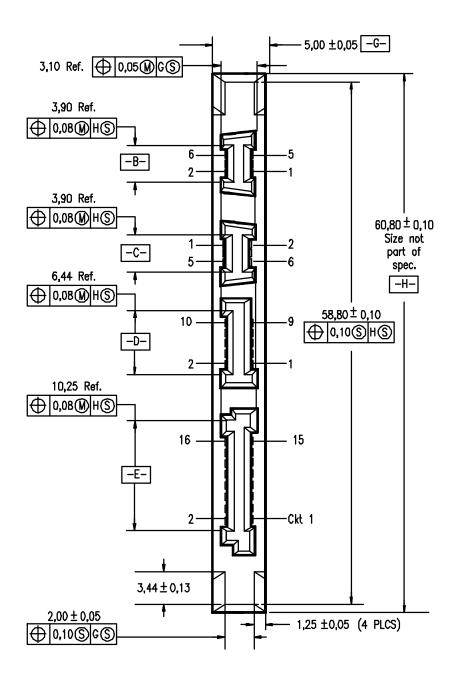

| 20  | Internal unitized backplane connector overview                               | .29 |

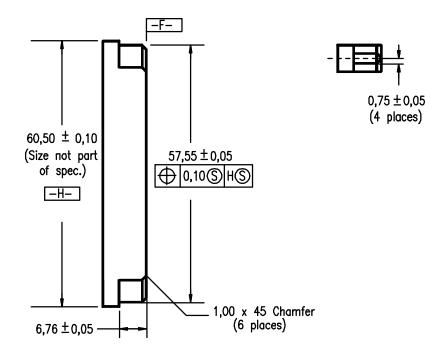

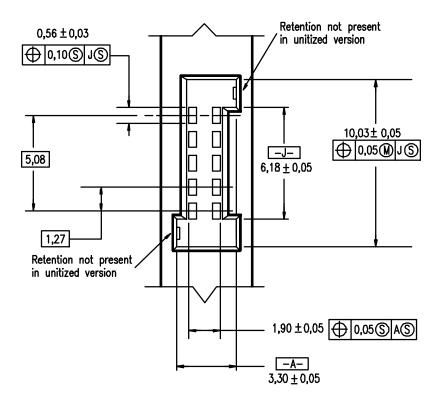

| 21  | Internal unitized backplane connector detail (side view)                     | .29 |

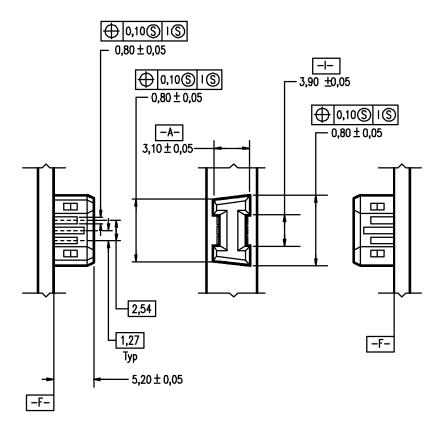

| 22  | Internal unitized backplane connector detail (end view)                      | .30 |

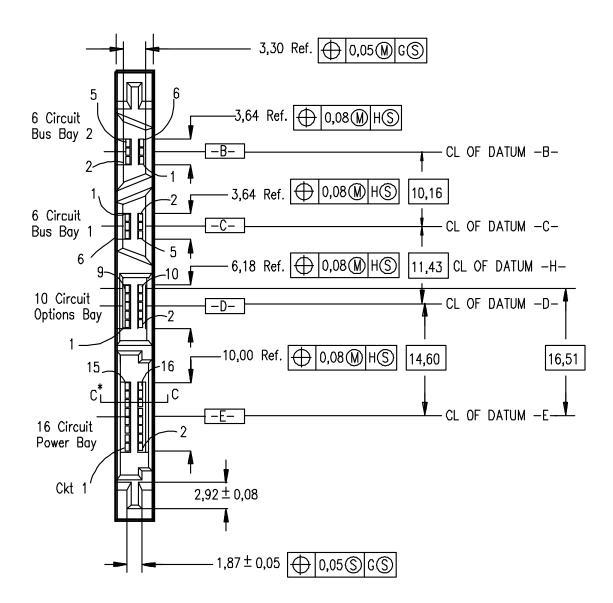

| 23  | Internal cable and backplane port connector detail                           | .31 |

| 24  | Internal cable and backplane option connector detail                         | .31 |

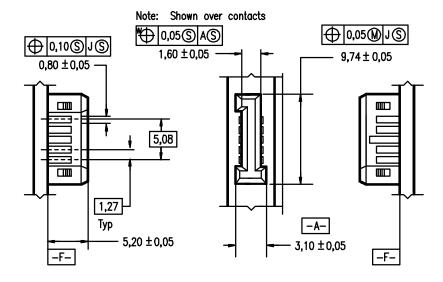

| 25  | Internal cable and backplane power connector detail                          | .32 |

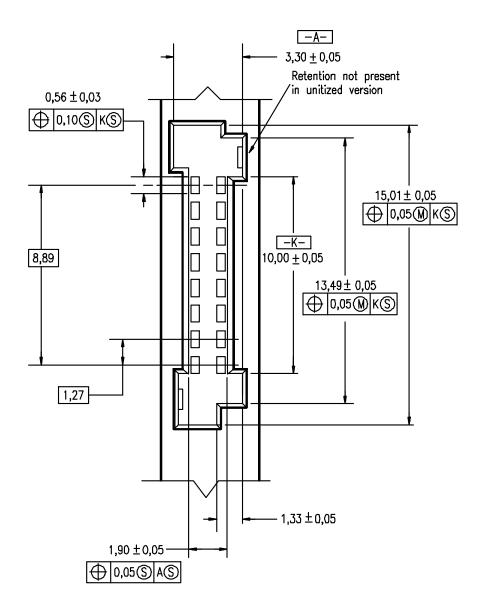

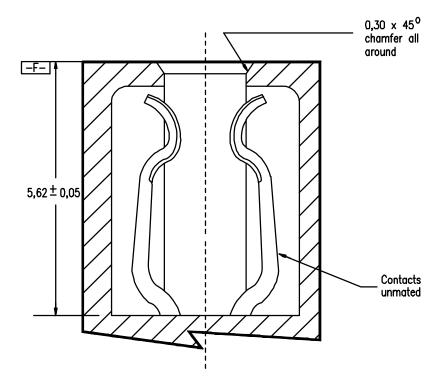

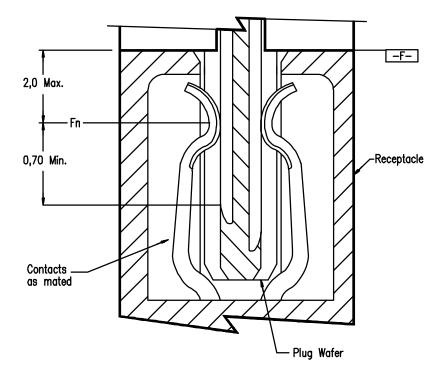

| 26  | Internal cable and backplane connector contact detail                        | .33 |

| 27  | Internal cable and backplane connector contact wipe detail                   | .33 |

| 28  | Internal cable and backplane port connector detail (2 ports shown)           | .34 |

| 29  | Internal cable and backplane option and power connector detail               | .35 |

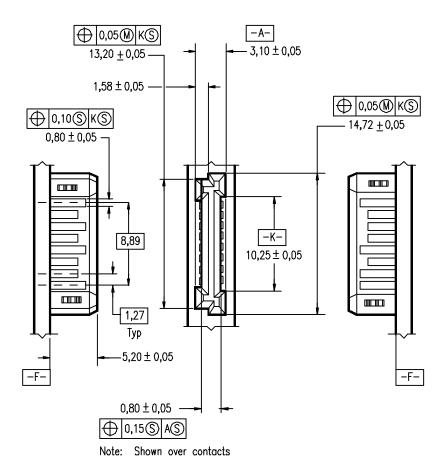

| 30  | Internal unitized device connector overview                                  | .36 |

| 31  | Internal unitized device connector detail (top view)                         | .37 |

| 32  | Internal unitized device connector detail (end view)                         | .38 |

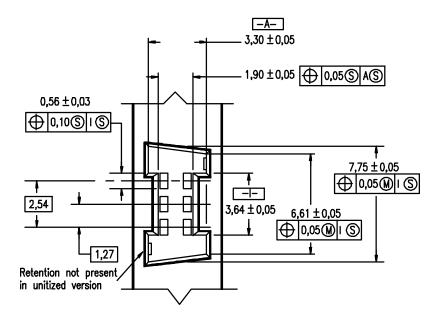

| 33  | Internal device port connector detail                                        | .39 |

| 34  | Internal device options connector detail                                     | .39 |

| 35  | Internal device power connector detail                                       | .40 |

| 36  | Internal device connector retention detail                                   | .41 |

| 37  | Internal device connector pin sequencing detail                              | .41 |

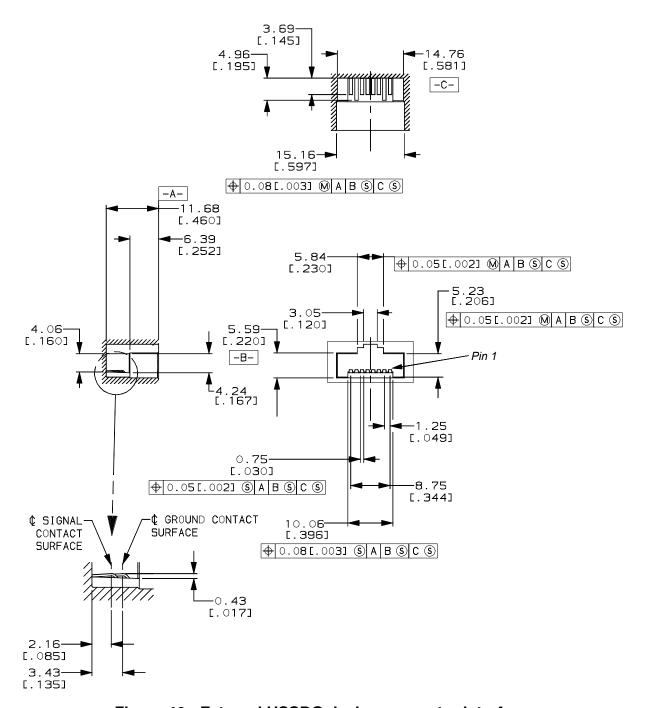

| 38  | External micro-miniature D device connector interface                        | .48 |

| 39  | External micro-miniature D cable connector interface                         | .49 |

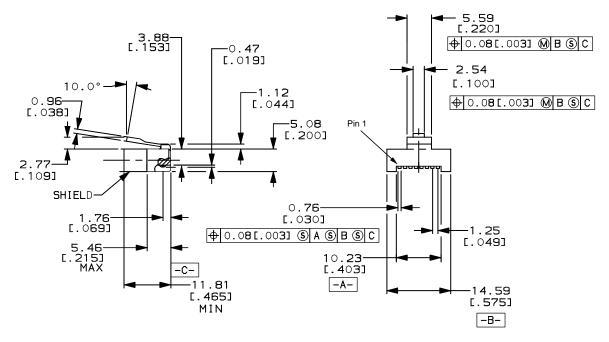

| 40  | External HSSDC device connector interface                                    | .52 |

| 41  | External HSSDC cable connector interface                                     | .53 |

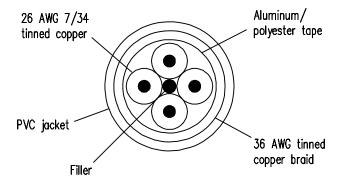

| 42  | Typical construction of external cable                                       | .54 |

| Anr | nexes                                                                        |     |

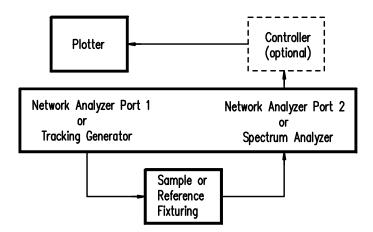

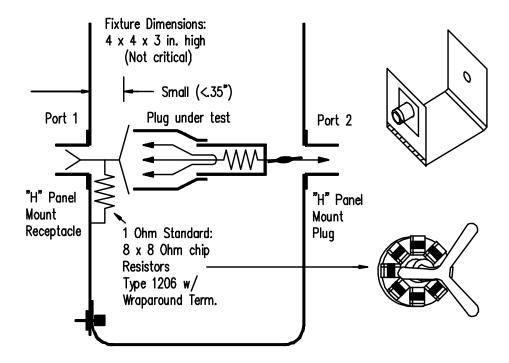

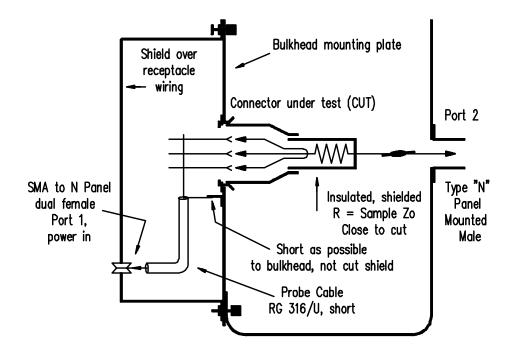

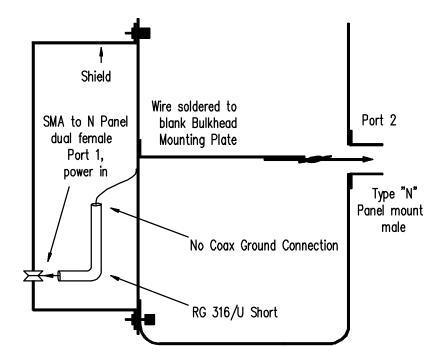

| Α   | Transfer impedance testing procedure                                         | .56 |

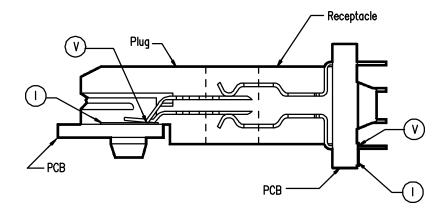

| В   | Internal connector testing procedure                                         | .62 |

| С   | External Micro-miniature D connector testing procedure                       | .69 |

| D   | External HSSDC connector testing procedure                                   | .79 |

| E   | Nulling of intersymbol jitter                                                | .81 |

| F   | Line fault detection scheme example                                          | .82 |

| G   | Circuit for degrading signal amplitude and introducing common mode levels    | .83 |

| Н   | Preferred test configurations for SSA links                                  | .85 |

| I   | Implementation guidelines                                                    | .86 |

| J   | Reference for copper, polymer dielectric, non-equalized SSA Cable Assemblies | .89 |

| K   | The use of Fiberoptic Port Connection Couplers With SSA                      | .91 |

#### Foreword (This foreword is not part of American National Standard X3.307-199x.)

This standard was developed by Task Group T10.1 of Accredited Standards Committee NCITS during 1996-97. The standards approval process started in 1997.

Annexes A through E are normative, annexes F through K are informative annexes and are not part of the standard.

Requests for interpretation, suggestions for improvement and addenda, or defect reports are welcome. They should be sent to the NCITS Secretariat, Information Technology Industry Council, 1250 Eye Street, NW, Suite 200, Washington, DC 20005-3922.

This standard was processed and approved for submittal to ANSI by Accredited Standards Committee on Information Technology, NCITS. Committee approval of the standard does not necessarily imply that all committee members voted for approval. At the time it approved this standard, the NCITS Committee had the following members:

James D. Converse, Chair Karen Higginbottom, Vice Chair Kate McMillan, Secretary

Organization Represented AMP Inc.

Apple Computer, Inc.

AT&T

Bull HN Information Systems, Inc Compaq Computers

Digital Equipment Corporation

Eastman Kodak Company

Hewlett-Packard

Hitachi America, Ltd.

Hughes Aircraft Company IBM Corporation

Institute for Certification of Computer Professionals (ICCP)

**Imation**

**Lucent Technologies**

National Communications Systems

National Institute of Standards and Technology

Neville and Associates

Panasonic Technologies

Share, Inc.

Storage Technology Corporation Sun Microsystems, Inc.

Name of Representative

Ben Bennett Edward Kelly (Alt.) David K. Michael

Jerry Kellenbenz (Alt.)

Thomas F. Frost Paul Bartoli (Alt.) Patrick L. Harris.

John Hill

Steve Park (Alt.) Scott K. Jameson

Richard Hovey (Alt.)

James D. Converse Michael Nier (Alt.)

Ms. Karen Higginbottom Donald C. Loughry (Alt.)

> John Neumann Kei Yamashita (Alt.)

Harold Zebrack

Ronald Sellitti Joel Urman (Alt.)

Kenneth Zemrowski

Philip E. Friedlund Herbert Bertine

Tom Rutt (Alt.)

Dennis Bodson William Olden (Alt.)

Frank McClelland (Alt.)

Michael D. Hogan Carlton Neville

Eric Johnson (Alt.) Stephen Heil Y. Machida (Alt.)

Gary Ainsworth

David Thewlis (Alt.)

Joseph S. Zajaczkowski Gary S. Robinson Sybase, Inc. Texas Instruments, Inc.

**Unisys Corporation**

U.S. Department of Defense

U.S. Department of Energy

Xerox Corporation

Donald R. Deutsch Clyde Camp Fritz Whittington (Alt.) Stephen P. Oksala Arnold Winkler (Alt.) Jerry L. Smith C.J. Pasquariello (Alt.) Ms. Carol S. Blackston Bruce R. White (Alt.) John Flannery Roy Pierce (Alt.) Technical Committee T10 on I/O Interfaces, which reviewed this standard, had the following members:

John B. Lohmeyer, Chair Lawrence J. Lamers, Vice-Chair Ralph Weber, Secretary

I. Dal Allan Tak Asami Geoffrey Barton Paul Boulay John Cannon Joe Chen Ms. Nancy Cheng Roger Cummings William Dallas Jan V. Dedek Mark Evans **Edward Fong** Raymond Gilson Dave Guss Kenneth J. Hallam Norm Harris Mike Hetzel Peter Johansson Skip Jones Thomas J. Kulesza Edward Lappin Robert Liu John Masiewicz Pete McLean Dr. Akira James Miura Ian Morrell Jay Neer Vit Novak Duncan Penman Kevin R. Pokorney Ron Roberts Steve D. Schueler Robert N. Snively

Arlan P. Stone

Roger Wang

Bob Whiteman

Devon Worrell

Matthew Thomas

Dennis Van Dalsen

Ruben Yomtoubian

Paul D. Aloisi Akram Atallah Robert Bellino Charles Brill Ting Li Chan Andy Chen Mike Chennery Chris D'Iorio Joe Dambach Dhiru N. Desai Timothy Feldman Edward A. Gardner Chuck Grant Peter Haas Dr. William Ham Edward Haske Stephen Holmstead Gerry Johnsen Richard Kalish Lawrence J. Lamers Pat LaVarre John Lohmeyer David McFadden Patrick Mercer E.J. Mondor John Moy Marc A. Noblitt **Erich Oetting** George Penokie Gary Porter Frank Samela J. R. Sims Jeff Stai Clifford E. Strang Jr. Pete Tobias Joseph Wach

Gary M. Watson

Anthony Yang

Jeffrey L. Williams

David Andreatta Wayne Baldwin Rick Bohn Michael Bryan Shufan Chan Jack Chen Dan Colegrove Zane Daggett Brian N. Davis Mike Eneboe Stephen G. Finch John Geldman Louis Grantham Douglas Hagerman Tom Hanan Stephen F. Heil Gerald Houlder Brian Johnson Greg Kapraun Dennis Lang Jaff Lin Bill Mable James McGrath Gene Milligan Charles Monia S. Nadershahi Tim Norman Dennis Pak Doug Piper Robert Reisch John P. Scheible Michael Smith Gary R. Stephens Nicos Syrimis Tokuyuki Totani Dean Wallace Ralph O. Weber Michael Wingard Danny Yeung

Task Group T10.1 on Serial Storage Architecture, which developed this standard, had the following members:

Lawrence J. Lamers, Chair John Scheible, Vice-Chair

Greg Alvey

Charles Brill

Wolfgang Drichelt

Bill Ham

Lawrence Lamers

Charles Monia

John Scheible

Daniel Tsai

Bob Atkinson David Deming Neil Edmunds Adge Hawes Bill Mable Brian Morissette Herb Silverman

Michael Wingard

Robert Bellino Mark DeWilde Chuck Grant Brad Kitson Gary Manchester Said Rahmani Kelly Tenuta

#### Introduction

This standard is divided into the following clauses and annexes.

Clause 1 defines the scope of the Serial Storage Architecture - PH2 (transport layer).

Clause 2 specifies the normative references.

Clause 3 defines the definitions, symbols, and abbreviations.

Clause 4 describes the conventions.

Clause 5 defines the modulation scheme.

Clause 6 defines the port data rate.

Clause 7 defines the electrical requirements.

Clause 8 defines the interconnection requirements.

Annexes A, B, C, D, and E are normative.

Annexes F, G, H, I, J, and K are informative.

American National Standard Information Technology -Serial Storage Architecture Physical Layer 2 (SSA-PH2)

#### 1. Scope

The SSA-PH2 standard (ANSI X3.307-199x) defines a physical layer that supports the SSA transport layer 2 (ANSI X3.308-199x), and any protocols supported by SSA-TL2 (ANSI X3.308-199x).

The goals of SSA-PH2 (ANSI X3.307-199x) are:

- a) extending the cable distance;

- b) copper cable operation at 40 MB/s;

- c) full duplex operation to achieve an aggregate 80 MB/s between two ports; and

- d) other capabilities that fit within the scope of SSA-PH2 (ANSI X3.307-199x) that may be proposed during the development phase by the participants in the project.

This document defines the SSA physical layer 2 (ANSI X3.308-199x) of the Serial Storage Architecture (SSA). SSA defines a serial interface hierarchy to be used for purposes within its distance and performance characteristics, including but not limited to storage subsystems. This standard is intended to be used with an upper layer protocol [e.g., SCSI-2 Protocol (ANSI X3.294-1996) or SCSI-3 Protocol (ANSI X3.309-199x)] and a transport layer [e.g., SSA Transport Layer 2 (ANSI X3.308-199x)].

A major goal of the SSA-PH2 standard (ANSI X3.307-199x) is to define a physical layer acceptable to device vendors, looking for an evolution from parallel SCSI or SSA-PH1 (ANSI X3.293-1996), and systems designers looking for opportunities to more fully exploit the capabilities inherent to a serial bus.

#### 1.1 SSA-PH2 characteristics

This standard defines the physical medium (e.g., encoding, modulation, clocking, line drivers/receivers, connectors, and cables).

The essential characteristics of SSA-PH2 (ANSI X3.307-199x) include:

- a) links using copper Cable Assemblies have been demonstrated to operate at 40 MB/s up to 20 m with on-chip CMOS drivers;

- b) support for optical transducers that allow longer distance connections;

- c) the link makes optimum use of the physical medium by using full-duplex communication to avoid arbitration overhead and turn-around delay;

- d) full duplex communication achieves an aggregate 80 MB/s bandwidth (40 MB/s in each direction) between two ports;

- e) the cables and connectors are physically compatible with small form factor devices;

- f) device connector capable of mating with both backplanes and cables;

- g) an electrically balanced design that reduces EMI and crosstalk; and

- h) a measurement scheme focusing on interoperability at separable connectors without requiring any internal physical access.

#### 1.2 SSA family of standards

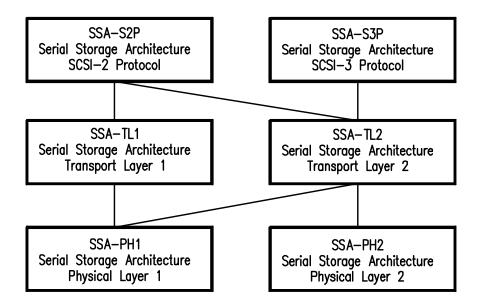

The relationships of the SSA family of standards is illustrated in figure 1.

Figure 1 - Relationship of the SSA standards

#### 1.2.1 SSA-S2P

Serial Storage Architecture - (SSA-S2P) SCSI-2 Protocol (ANSI X3.294-1996) defines the SCSI-2 Protocol used to run on top of the SSA transport layers 1 or 2.

#### 1.2.2 SSA-S3P

Serial Storage Architecture - (SSA-S3P) SCSI-3 Protocol (ANSI X3.309-199x) defines the SCSI-3 Protocol used to run on top of the SSA transport layer 2.

#### 1.2.3 SSA-TL1

Serial Storage Architecture - (SSA-TL1) Transport Layer 1 (ANSI X3.295-1996) defines the Transport layer that runs SSA-S2P and runs on SSA-PH1.

#### 1.2.4 SSA-TL2

Serial Storage Architecture - (SSA-TL2) Transport Layer 2 (ANSI X3.308-199x) defines the Transport layer that runs SSA-S2P and SSA-S3P and run on SSA-PH1 or SSA-PH2.

#### 1.2.5 SSA-PH1

Serial Storage Architecture - (SSA-PH1) Physical Layer 1 (ANSI X3.293-1996) defines the Physical layer that runs SSA-TL1 and SSA-TL2, and consists of the electrical characteristics of the interface and the connectors.

#### 1.2.6 SSA-PH2

Serial Storage Architecture - (SSA-PH2) Physical Layer (ANSI X3.307-199x) defines the Physical layer that runs SSA-TL2, and consists of the electrical characteristics of the interface and the connectors.

#### 2. References

#### 2.1 Normative references

The following standards contain provisions which, through reference in this text, constitute provisions of this American National standard. At the time of publication, the editions indicated were valid. All standards are subject to revision, and parties to agreements based on this American National standard are encouraged to investigate the possibility of applying the most recent editions of the standards listed below.

Members of IEC and ISO maintain registers of currently valid International Standards, and ANSI maintains registers for American National Standards.

ANSI/EIA 364 (1994) - Electrical Connectors Test Procedure. (parts 13, 20, 21, 23, 31, 41, and 46)

IEC 512: (19xx) - Electromechanical components for electronic equipment; basic testing procedures and measuring methods

IEC 512-2 (1985) Part 2 - Insulation resistance

IEC 512-4 (1976) Part 4 - Dynamic stress tests

IEC 512-5 (1992) Part 5 - Impact tests (free components), static load tests (fixed components), endurance tests and overload tests

IEC 512-6 (1984) Part 6 - Climatic tests and soldering tests

IEC 512-7 (1993) Part 7 - Mechanical operating tests and sealing tests

IEC 512-11-7 (1996) Part 11 - Climatic tests - Test 11g: Flowing mixed gas corrosion test

IEC 801 (1988) Environmental testing

ANSI X3.308-199x - Information Technology - Serial storage architecture - Transport layer 2 (SSA-TL2)

#### 2.2 Informative references

The following related standards are for informational purposes only, and do not contain provisions of this standard. At the time of publication, the edition indicated was valid. All standards are subject to revision, and parties to agreements based on this standard are encouraged to investigate the possibility of applying the most recent editions of the standard listed below. Members of IEC and ISO maintain registers of currently valid International Standards, and ANSI maintains registers for American National Standards.

ANSI X3.293:1996 - Information Technology - Serial Storage Architecture - Physical Layer 1 (SSA-PH1)

ANSI X3.295:1996 - Information Technology - Serial Storage Architecture - Transport Layer 1 (SSA-TL1)

ANSI X3.294:1996 - Information Technology - Serial Storage Architecture - SCSI-2 Protocol (SSA-S2P)

ANSI X3.309-199x - Information Technology - Serial Storage Architecture - SCSI-3 Protocol (SSA-S3P)

EN50082-1 - Generic ESD immunity standard

Further information regarding the implementation of this standard may be available at http://www.ncits.org/t10 or http://www.ssaia.org.

#### 3. Definitions, symbols, and abbreviations

#### 3.1 Definitions

- **3.1.1. application:** A process that is communicating via the link.

- **3.1.2. cable:** A uniform media between connectors containing the four conductors required for two lines.

- 3.1.3. cable assembly: A cable with connectors, backshells, and retention schemes on each end.

- **3.1.4. character:** A sequence of 10 encoded bits that represents a data byte or a protocol function.

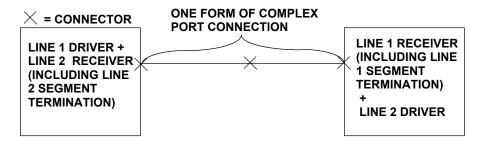

- 3.1.5. complex port connection: Any means of connecting ports other than a single Cable Assembly

- **3.1.6. frame:** A sequence of 4 or more data characters surrounded by FLAG characters.

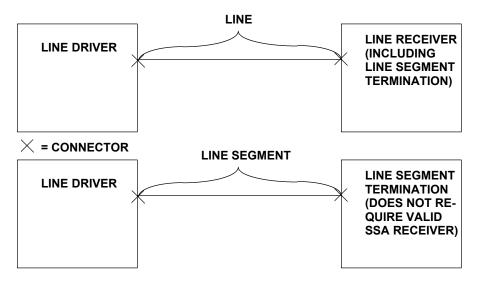

- **3.1.7. line:** The pair of balanced electrical conductors connecting (1) the positive side of the line driver port connector to the positive side of the line receiver port connector and (2) the negative side of the line driver port connector to the negative side of the line receiver port connector.

- **3.1.8. line+:** The line conductor connecting the positive side of the line driver port connector to the positive side of the line receiver port connector.

- **3.1.9. line-:** The line conductor connecting the negative side of the line driver port connector to the negative side of the line receiver port connector.

- **3.1.10. line driver:** The electrical circuitry that set the logical state of the line at the port connector.

- **3.1.11. lineIn+:** The line receiver connection to the Line+ conductor.

- **3.1.12. lineIn-:** The line receiver connection to the Line- conductor.

- **3.1.13. lineOut+:** The line driver connection to the Line+ conductor.

- **3.1.14. lineOut-:** The line driver connection to the Line- conductor.

- **3.1.15. line receiver:** The electrical circuitry that detect the logical state of the line at the port connector including Line Segment Termination. The Line Receiver shall be capable of reporting bit errors.

- **3.1.16. line segment:** That portion of a Line between Line Driver and the Line Segment termination.

- **3.1.17. line segment termination:** The electrical properties of the load on the end of the line segment opposite the end associated with the Line Driver.

- **3.1.18. link:** The serial connection between ports on two devices including the Line Drivers, Line Receivers, and the associated Cable Assembles.

- 3.1.19. node: A system, controller, or device with one or more ports.

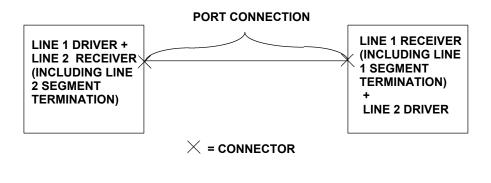

- **3.1.20.** port: A line driver and a line receiver operating together on a device (two lines, four conductors).

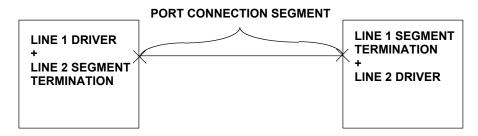

- **3.1.21. port connection:** The combination of two lines that tie the line driver in a port to the line receiver in the another port and the line driver in the other port to the line receiver in the first port.

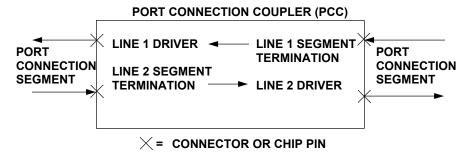

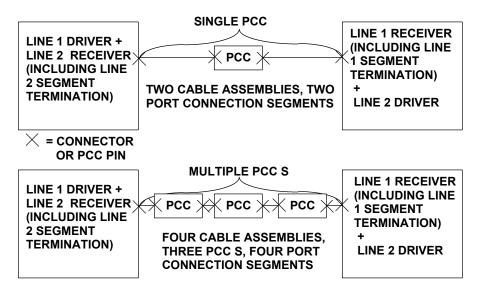

- **3.1.22. port connection coupler:** A device that ties two Port Connection segments together.

- **3.1.23. port connection segment:** A portion of a Port Connection that ties a line driver to a line segment termination on one line and a line driver to a line segment termination in the other line.

#### 3.2 Symbols and abbreviations

AWG American wire gauge

**BER** bit error rate

CMOS complementary metal oxide semiconductor

CRC cyclic redundancy check

CUT connector under test

DMA direct memory access

DUT device under test

EMI electro-magnetic interference

ERP error recovery procedure

ESD electro-static discharge

FCS fiber channel standard

**FDDI** fiber distributed data interface **FSN** frame sequence number

**HSSDC** high speed serial data connector insulation displacement connector

LED Light Emitting Diode

LFT Line Fault Threshold

LSI large scale integration

NRZ non-return-to-zero

PCC Port Connection Coupler

POR power-on reset power-on self-test

**RAS** reliability, availability, and serviceability

**RFI** radio-frequency interference

**RH** relative humidity

RLFT Receiver Line Fault Threshold receive sequence number

SCSI Small Computer Systems Interface

$\begin{array}{lll} \textbf{SSA} & \textbf{Serial Storage Architecture} \\ \textbf{TSN} & \textbf{transmit sequence number} \\ \textbf{SMS} & \textbf{SSA Message Structure} \\ \textbf{V}_{it} & \textbf{Voltage of LineIn termination} \\ \textbf{V}_{ot} & \textbf{Voltage of LineOut termination} \\ \end{array}$

& Logical AND

Assignment or comparison for EQUAL

Comparison for NOT EQUALComparison for LESS THAN

≤ Comparison for LESS THAN OR EQUAL TO

> Comparison for GREATER THAN

+ ADD

- SUBTRACT

\* MULTIPLY

± PLUS OR MINUS

≈ APPROXIMATELY

>> MUCH GREATER THAN

#### 4. Conventions

Certain words and terms used in this standard have a specific meaning beyond the normal English meaning. These words and terms are defined either in the glossary or in the text where they first appear. Lower case is used for words having the normal English meaning.

Fields containing only one bit are usually referred to as the "named" flag instead of the "named" field. When a bit is set its value is 1. When a bit is cleared, its value is 0.

Numbers that are not immediately followed by lower-case "b" or "h" are decimal values. Numbers immediately followed by lower-case "b" (xxb) are binary values. Numbers immediately followed by lower-case "h" (xxh) are hexadecimal values. Decimal numbers are indicated with a comma (e.g., two and one half is

represented as "2,5"). Decimal numbers having a value exceeding 9999 are represented with a space (e.g., 2345 and 12 345).

In circuit diagrams, a T intersection implies a connection, a + implies no connection, and a + with a dot at the crossover implies a connection.

In case of conflict, figures take precedence over tables, and both figures and tables take precedence over text.

#### 5. Modulation

The encoded data is transmitted as a base-band digital signal using the non-return-to-zero (NRZ) method.

#### 6. Data rate

SSA links operate at a data rate of either 40 MB/s (i.e., 400 Mb/s) or 20 MB/s (i.e., 200 Mb/s) on the line.

The transmit clock shall be accurate to  $\pm$  250 PPM.

The receiver shall acquire bit synchronization from the transitions in the transmitted data. If an asynchronous sampling technique is used then the design shall take metastability into account.

#### 7. Electrical requirements

SSA may be implemented with a number of different physical schemes. In this standard only the AC coupled copper version is defined. Future standards may define alternate media and electrical interfaces. The requirements apply to both internal and external interconnections (except that the shielding requirements do not apply for internal).

Table 1 shows the physical schemes that are compatible with the SSA protocol.

Table 1 - SSA physical interconnect schemes

| Physical scheme         | Internal      | External      |

|-------------------------|---------------|---------------|

| Directly coupled copper | SSA-PH1       | SSA-PH1       |

| AC coupled copper       | This standard | This standard |

NOTE 1 - The AC coupled scheme specified in this standard is compatible with devices implemented using the SSA-PH1 standard directly coupled copper scheme, if the SSA-PH1 receiver input range includes  $V_{it} \pm 650$  mV.

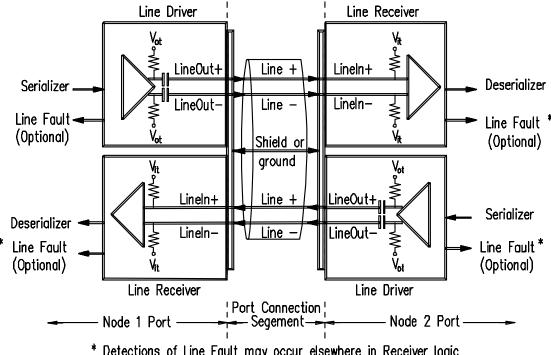

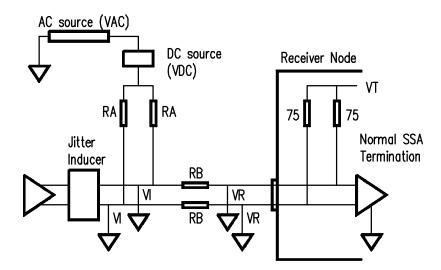

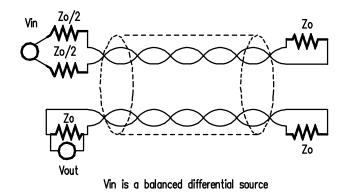

The electrical configuration of the serial link is shown in figure 2.

\* Detections of Line Fault may occur elsewhere in Receiver logic

Figure 2 - Electrical configuration for SSA serial links

The electrical requirements are defined in a modular way so that each of the three basic components of the serial link are individually defined. The three basic components are the Line Driver, Port Connection, and the Line Receiver. The boundaries of these components are chosen so that the requirements apply at the separable connectors on the ports.

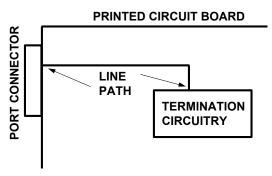

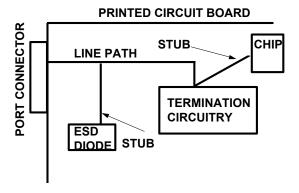

In order to minimize transmission line reflections the characteristic impedance measured at the LineIn+ and LineIn- pins shall meet the requirements in 7.3, the characteristic impedance measured at LineOut+ and LineOut- shall meet the requirements of 7.1.6.1, and the characteristic impedance of the Port Connection shall meet the requirements of 7.5. This measurement is affected by the details of the electrical path between the device connector pins and the terminating resistor near the receiver.

The test conditions defined create an electrical environment that approximates worst case noise and loading. In order to present a more complete noise exposure, specific activity on ports not directly under test is also required during the test execution. These test conditions reveal degradation caused by improper stubs, excessive cross talk, excessive series inductance, inadequate decoupling, and other effects that may be caused by inappropriate design.

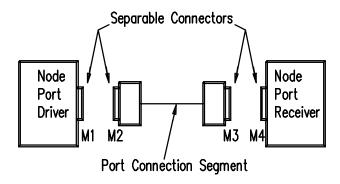

The test points that apply are shown in figure 3. The Line Driver requirements are verified at M1. Inputs to verify the line requirements are measured at M2. Outputs for the Line requirements are verified at M3. Inputs to verify the Line Receiver characteristics are verified at M4.

Figure 3 - Test points

In order to assist inter-operability between ports designed or manufactured under different conditions, the Line Driver, Port Connection, and Line Receiver shall each satisfy their respective requirements. See 7.5 for requirements applying to complex lines, including Lines using repeaters, equalizers, and other non-homogeneous schemes between M2 and M3.

The overall performance requirement on the system is a bit error rate less than 10<sup>-12</sup> (e.g., less than one error in 10<sup>12</sup> bits transferred). In order to allow for system noise not present during the Line Receiver requirements test, the Line Receiver itself shall not exceed a bit error rate of 10<sup>-13</sup> with the defined inputs (see 7.2.4) at M4.

The pulses and waveforms are defined in terms of the differential voltage observed at specific points with specific loads, even though SSA uses current drivers. Measuring the required differential currents is beyond the present state of the measurement art. All references to timing are made with respect to the differential voltage signals.

#### 7.1 Line driver

#### 7.1.1 General description

An SSA line driver is a circuit that converts logic signals from the serializer into differential currents to drive the outbound lines.

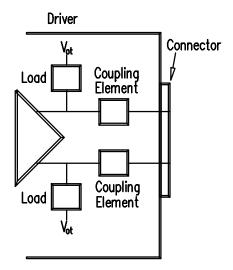

The SSA line driver shall deliver balanced currents to the line. Balance is achieved when the di/dt in the Line+ conductor is identical in magnitude but opposite in sign to the di/dt in the Line- conductor at the same point in time and space. Current balance is needed to keep the signal return currents off the external shield (for EMI reasons) and away from the other SSA signal paths in the cable (for cross talk reasons). The amount of imbalance that is tolerable is not defined in this standard because the cross talk effects are covered by the requirements on the Line Drivers, Port Connection, and Line Receivers. The EMI effects are dependent on the system configuration and the interconnect shielding used.

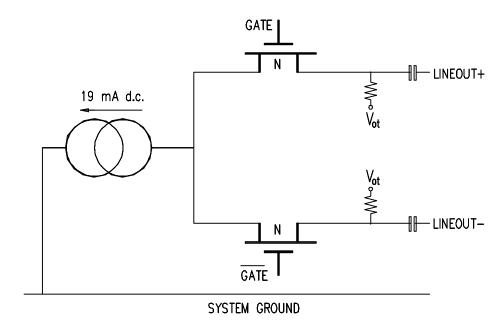

To ensure balanced currents from the Line Driver, the Line Driver shall contain a single current source (sink) whose output shall be connected to the Line Driver internal Load and the internal Coupling Element, and shall be directed to Line+ through the LineOut+ connection and to Line- through the LineOut- connection in such a manner that the sum of the currents in both lines nominally equals half the current source output at all times. The total current (current source output) is nominally 19 mA d.c. and is designated  $I_t$ . The current in Line+ is designated  $I_t$  and the current in Line- is designated  $I_t$ . Nominally  $I_t = (I_t + I_t)/2$  which requires a balanced condition,  $dI_t / dt = -dI_t / dt$ .

The Line Driver shall have sufficient voltage conformance to accommodate ground shift between the two ports (see 7.4).

Figure 4 shows one possible implementation of a Line Driver. The current source output is distributed to the line using the N channel transistors. Notice that even if the properties of the transistors or of the signals

Figure 4 - SSA Line Driver implementation example

driving the transistor gates are not identical that the balance condition still exists on the line.

The properties of these current steering transistors and their control signals need to be carefully controlled to meet other driver requirements such as slew rate, spectral content, and jitter.

In general, balanced transmissions are aided by ensuring that the properties of Line+ are identical to the properties of Line-.

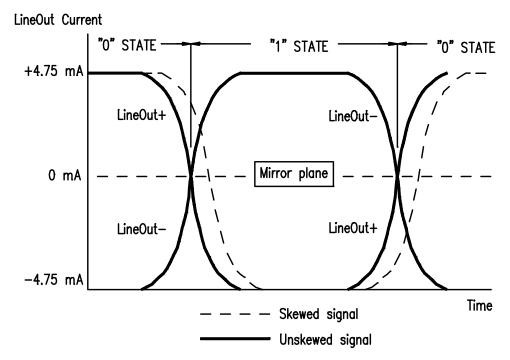

Figure 5 shows the relationship of the currents existing during signal transitions. Transmission is balanced if mirroring through the mirror plane shows no new traces. Time skew produces significant imbalance.

Figure 5 - Relationship between LineOut currents at the port connector

#### 7.1.2 Driver line fault detection

The line driver may indicate a line fault when certain line conditions exist. These conditions are left to the implementer to determine.

Reporting of line faults is a function of the transport layer (see SSA-TL2).

#### 7.1.3 Test conditions for line drivers

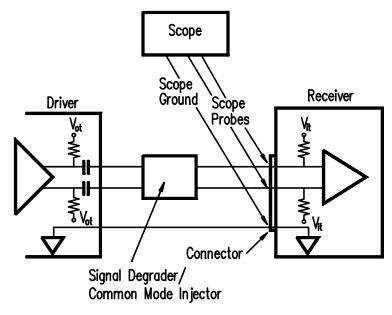

All Line Driver measurements are referenced to the Port Connector.

#### 7.1.3.1 General requirements

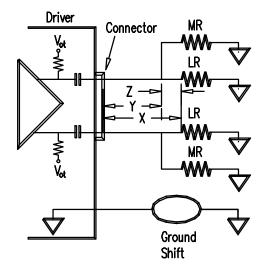

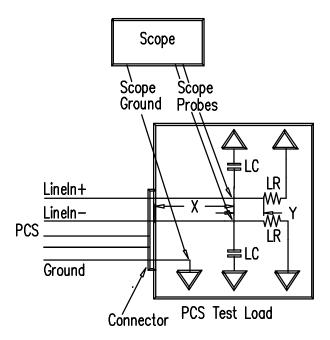

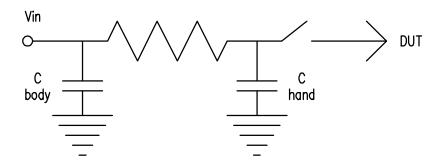

Line drivers shall be tested using the test circuit shown in figure 6. The distance between the port connector and the load resistance LR (labeled X in figure 6) shall not exceed 5 cm. The distance between the measurement point (at the LR and MR junction) and the load resistance LR (labeled Z in figure 6) shall not exceed 5 mm. The difference between the connector to measurement point distance (labeled Y in figure 6) of the LineOut+ and LineOut- lines of the driver shall not exceed 5 mm. The resistance of the combined load resistance LR and measurement resistance MR shall be 75  $\Omega \pm 2\%$ . The total additional capacitive load from the scope probing scheme between Line+ and ground and between Line- and ground at the port connector shall be a maximum of 1,5 pF. This capacitance includes the sensing probes and equipment added to enable probing. The load shall conform to the characteristic impedance requirements in 7.3 at its connector.

Figure 6 - Test environment for drivers

The measurement procedure shall be performed as follows.

- a) The measurement system bandwidth including preamplifier and probes shall be adequate for the 5th harmonic of the highest frequency square wave;

- b) Trigger on the rising edge of single-ended true (logical 1) output with a minimum of 5 and a maximum of 35 data bit times delay after the trigger edge prior to the measurement. This delay is required to capture data dependent jitter caused by intersymbol interference. This test returns twice the actual jitter due to the data edge triggering. The actual jitter value (half that measured above) shall be used when determining conformance;

- c) Driver waveform shall be measured as a differential voltage with an accuracy of ±10 mV.

The data pattern shall consist of continuous contiguous K28.5 characters resulting in a character stream with alternating running disparity. This pattern contains maximum and minimum run lengths (both high and low) and therefore is a worst case pattern. All SSA ports shall be capable of running this pattern continuously. A mechanism shall be implemented in all SSA ports to enable the continuous contiguous K28.5 transmissions required for these tests at all supported speeds.

The test environment shall include electrical activity on the device typical of the intended applications environment. All ports on the node shall be active during the driver test. Continuous K28.5 characters shall be presented to the receive side of the port used for the driver test. All inputs should originate from drivers that conform to this standard.

#### 7.1.3.2 Driver jitter

The maximum allowed Line driver jitter is defined in 7.1.5. The line driver jitter shall be measured under the test conditions defined in 7.1.2. The jitter shall be measured at the zero differential voltage level as a peak-to-peak value for the population sampled. The maximum value for this measured jitter (due to the triggering method) is twice the actual jitter defined in table 5.

#### 7.1.3.3 Driver slew rate

The maximum allowed driver slew rate is defined in 7.1.5.

The line driver slew rate shall be measured under the conditions defined in 7.1.3.1 and as follows:

a) measurement system bandwidth sufficient to measure the slew rate defined in 7.1.5;

b) slew rate of the most probable curve from multiple samples of the waveform between ±200 mV differential voltage levels.

#### 7.1.3.4 Line driver output spectral content

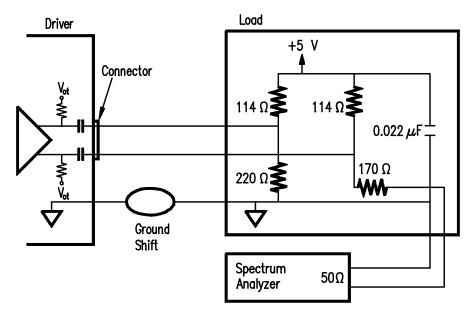

The line driver output spectral content shall be measured under the test conditions defined in 7.1.3.1 with the following changes;

- a) the load shall consist of the circuit shown in figure 7 and shall conform to 7.3;

- b) the capacitive load to logic ground on each side of the driver port shall be minimized and shall be less than 2 pF;

- c) the ground shift shall consist of -0,5 V d.c. to +0,5 V d.c. only;

- d) both the LineOut+ and LineOut- shall be independently measured (figure 7 shows the measurement of only one LineOut).

Figure 7 - Test environment for driver spectral content

The maximum allowed line driver output spectral content is defined in 7.1.5.

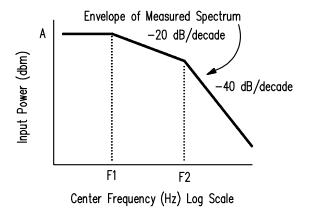

The line driver output spectrum shall be within the shaded area of figure 9 using the data points from table 2 using a detection bandwidth of 10 kHz over the frequency range d.c. to 1,0 GHz for the 200 Mb/s speed and d.c. to 1,5 GHz for the 400 Mb/s speed. The envelope of the measured spectrum shall be used to determine the intensity of the spectral content as shown in figure 8.

Figure 8 - Driver output spectral content

Table 2 - Driver output spectral content

| Speed    | F1      | F2      | Α       |

|----------|---------|---------|---------|

| 400 Mb/s | 160 MHz | 636 MHz | -11 dBm |

| 200 Mb/s | 80 MHz  | 318 MHz | -11 dBm |

#### 7.1.4 Pulse mask for SSA drivers

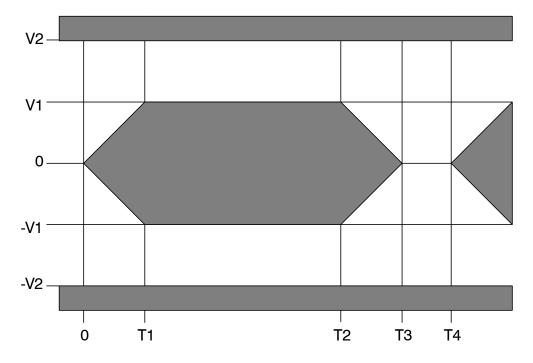

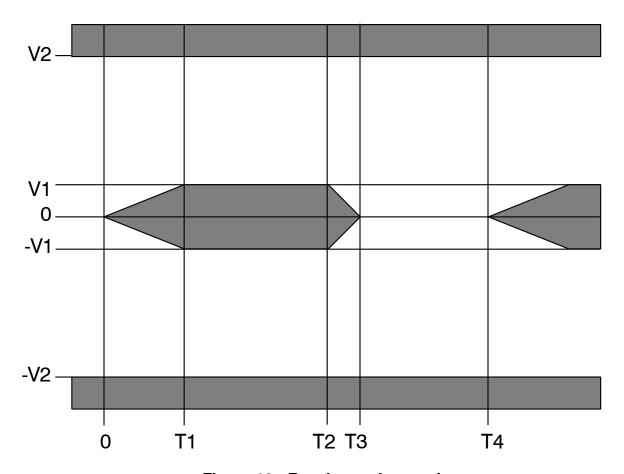

The differential voltage measured using the test circuit, measurement equipment, data patterns, and test environment defined in 7.1.2 shall remain outside the shaded area and be wholly contained between the V2 and -V2 voltage levels of the pulse mask shown in figure 9.

Figure 9 - SSA driver pulse mask

Table 3 contains the requirements when triggering from the source clock.

**Table 3 - Driver system operating parameters**

| Speed    | V1     | V2      | T1      | T2      | Т3      | T4      |

|----------|--------|---------|---------|---------|---------|---------|

| 400 Mb/s | 500 mV | 1000 mV | 0,25 ns | 2,05 ns | 2,30 ns | 2,50 ns |

| 200 Mb/s | 500 mV | 1000 mV | 0,25 ns | 4,47 ns | 4,72 ns | 5,00 ns |

Table 4 contains the requirements when triggering as specified in 7.1.3.1.

**Table 4 - Driver test parameters**

| Speed    | V1     | V2      | T1      | T2      | Т3      | T4      |

|----------|--------|---------|---------|---------|---------|---------|

| 400 Mb/s | 500 mV | 1000 mV | 0,25 ns | 1,85 ns | 2,10 ns | 2.50 ns |

| 200 Mb/s | 500 mV | 1000 mV | 0,25 ns | 4,19 ns | 4,44 ns | 5,00 ns |

#### 7.1.5 Line driver operating requirements

The operating requirements for the line driver are summarized in table 5.

Table 5 - Line driver operating requirements at the port connector

|                                                                   |                                        | •                   |                       |  |

|-------------------------------------------------------------------|----------------------------------------|---------------------|-----------------------|--|

| Line driver requirements:                                         | minimum                                | nominal             | maximum               |  |

| Output current peak to peak (s)                                   | 8,1 mA                                 | 9,5 mA              | 10,9 mA               |  |

| Output current imbalance (LineOut+ - LineOut-) (s)                | -0,5 mA                                |                     | +0,5 mA               |  |

| Off state output d.c. current (s)                                 | -25 μA                                 |                     | +25 μΑ                |  |

| LineOut+ leakage current to ground                                |                                        |                     | 10 μA d.c.            |  |

| LineOut- leakage current to ground                                |                                        |                     | 10 μA d.c.            |  |

| Output termination voltage (V <sub>ot</sub> )                     | 2.97V                                  |                     | 5.5 V                 |  |

| a.c. component of V <sub>ot</sub> (peak to peak) as measured from |                                        |                     | 100 mV from           |  |

| Logic Ground to V <sub>ot</sub> .                                 |                                        |                     | 30 Hz to 6 MHz        |  |

|                                                                   |                                        |                     | 50 mV from            |  |

|                                                                   |                                        |                     | 6 MHz to 500          |  |

|                                                                   |                                        |                     | MHz                   |  |

| Output voltage slew rate (d)                                      | 2,0 V/ns                               |                     | 5,0 V/ns              |  |

| Output jitter at 200 Mb/s (peak-peak) 1 (d)                       |                                        |                     | 0,28 ns               |  |

| Output jitter at 400 Mb/s (peak-peak) 1 (d)                       |                                        |                     | 0,20 ns               |  |

| Output voltage spectral content (s)                               | Shall be within the conditions defined | . ,                 | ire 8) under the test |  |

| Output voltage waveform (d)                                       | Shall be within pul                    | se mask (see figure | e 9) under test       |  |

|                                                                   | conditions defined in 7.1.2            |                     |                       |  |

| Ground shift                                                      | Shall comply with 7.4                  |                     |                       |  |

| NOTE 1. This is an appreting requirement. It is the actual if     | ttor allowed under a                   | otom operating as   | nditiona It is not    |  |

NOTE <sup>1</sup> - This is an operating requirement. It is the actual jitter allowed under system operating conditions. It is not the result of the tests defined in 7.1.2 because of the triggering scheme used for these tests. The test conditions in 7.1.2 result in the observed jitter being twice the value defined in this table.

(s) = single-ended, (d) = differential

Drivers shall tolerate single-ended voltage inputs from -0,5 to +4,13 V applied through  $75\Omega \pm 1\%$  without damage in a power off state. The 4,13 V level is derived from the 3,63 V level (table 9) plus 0,5 V ground shift.

#### 7.1.6 Other Line Driver requirements

Figure 10 illustrates the schematic of the Line Driver termination.

Figure 10 - Line Driver termination schematic

#### 7.1.6.1 Line Driver termination

The Line driver termination is defined in terms of TDR impedance in the same way as Line Segment termination except it is measured at the Port connector LineOut pins (see 7.3). Table 6 specifies the Line Driver termination requirements.

| TABLE & ELECTRIC                 | on requirements for Emic . |             |                 |

|----------------------------------|----------------------------|-------------|-----------------|

| Receiver port test configuration | TDR rise time max (ps)     | Zo max (Ωs) | Zo min (Ωs)     |

| LineOut+ to logic ground         | 375                        | 90          | 60 <sup>1</sup> |

| LineOut- to logic ground         | 375                        | 90          | 60 <sup>1</sup> |

|                                  |                            |             |                 |

180

120 <sup>1</sup>

Table 6 - Electrical requirements for Line Driver termination

375

#### 7.1.6.2 Line Driver internal load

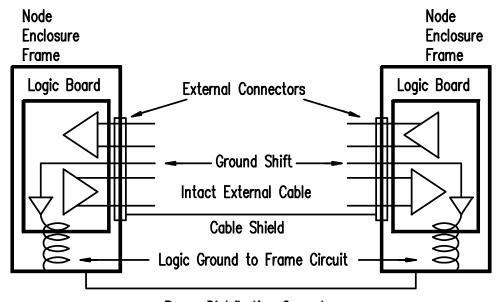

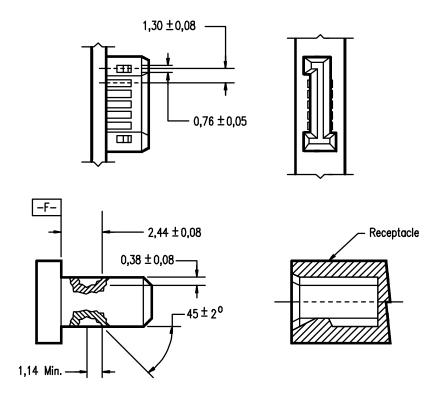

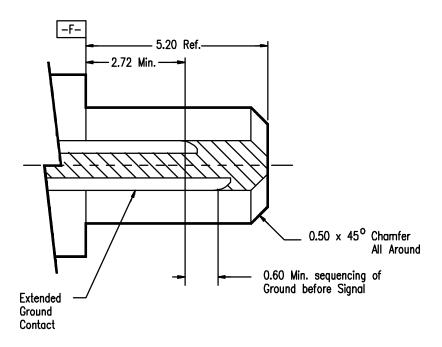

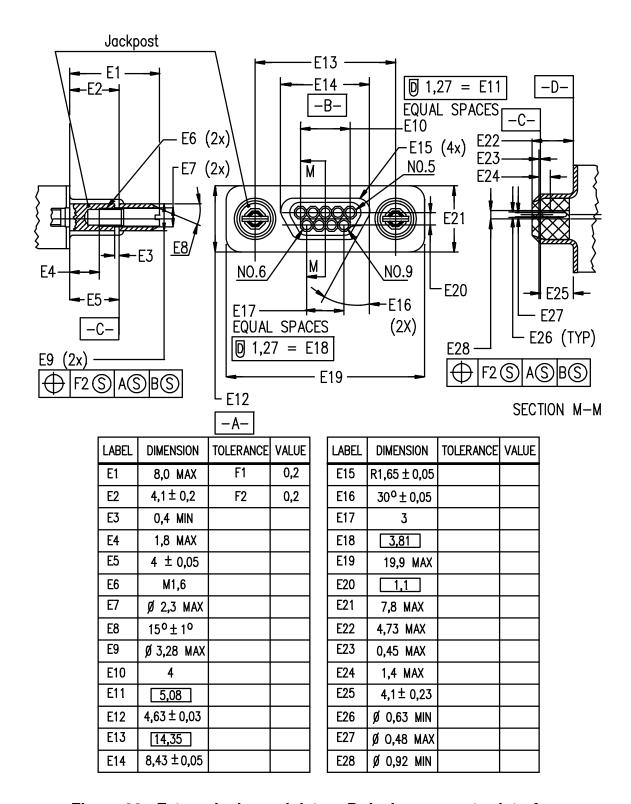

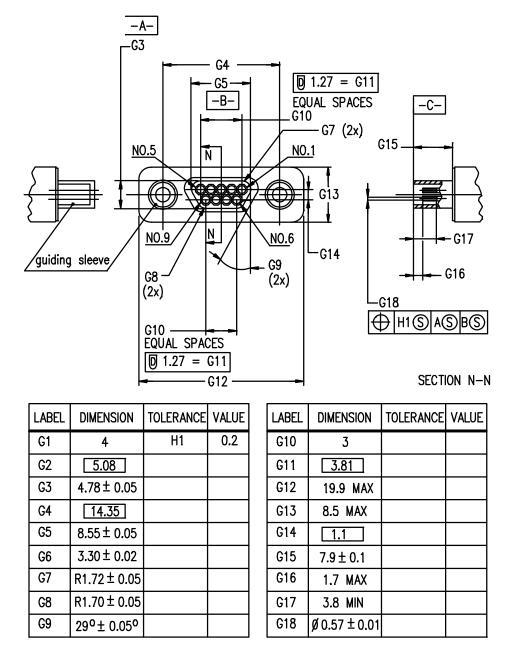

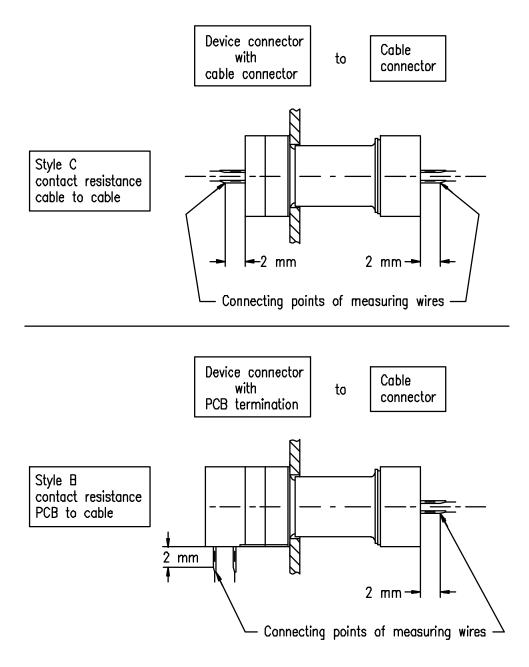

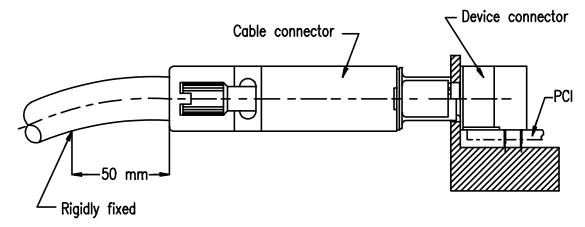

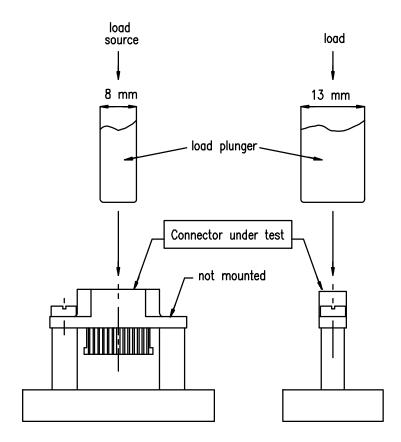

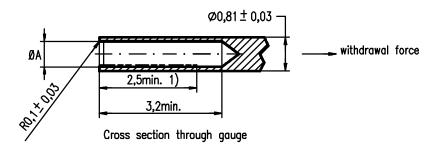

LineOut+ to LineOut-